- Vhdl program for left shift register how to#

- Vhdl program for left shift register pdf#

- Vhdl program for left shift register serial#

- Vhdl program for left shift register manual#

Vhdl program for left shift register serial#

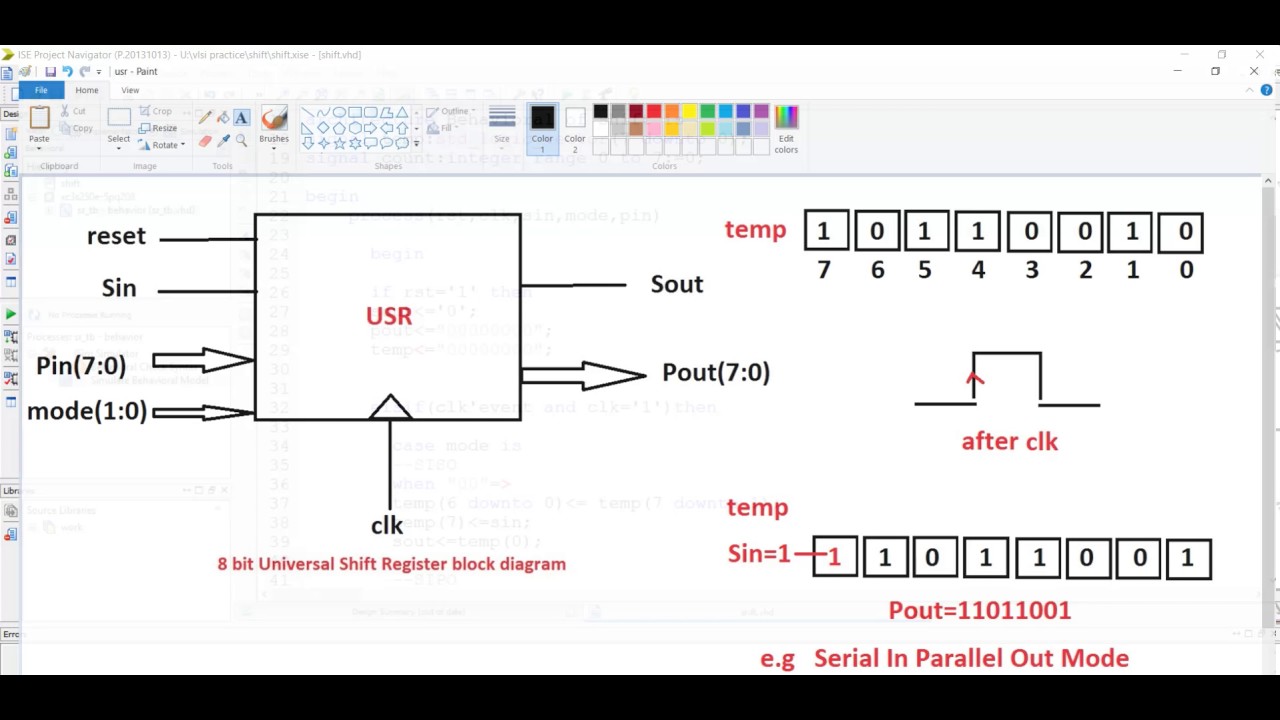

std_logic_1164.all entity shift is port(C, SI: in std_logic SO: out std_logic) end shift architecture archi of shift is signal tmp: std_logic_vector(7 downto 0) begin process (C) begin if (C'event and C='1') then for i in 0 to 6 loop tmp(i+1) = tmp(i) end loop tmp(0) = SI end if end process SO = tmp(7) end archi Following is the VHDL code for an 8- bit shift- left reg ister with a negative-edge clock, clock enable, serial in, and serial out. A serial-in, serial-out shift register.įollowing is the VHDL code for an 8-bit shift-left register with a Following is the VHDL code for an 8- bit shift- left reg ister with a positive-edge clock, serial in, and serial out. They will store a bit of data for each register. Design of Serial IN - Serial Out Shift Register u. Design of Serial In - Parallel Out Shift Register. Serial-in, serial-out shift registers delay data by one clock time for each stage. Modeling Styles in VHDL Design of Parallel IN - Parallel OUT Shift Regist.

Vhdl program for left shift register pdf#

Vhdl Code for Serial in Serial Out Shift Register Using Behavioral Modelling - Free download as Word Doc (.doc /.docx), PDF File (.pdf). Related items such as accessories, repair parts, etc. The left-most hexadecimal digit is the most significant bit. A shift register can be initialized in VHDL or Verilog code for both synthesis and simulation. Using Look-Up Tables as Shift Registers (SRL16). The program applies only to Automower® units. A shift register has the capability of shifting the data stored in the register from left to right or right to left. VHDL Code for 4-Bit Shift Register 1 Parallel In Parallel Out Shift Registers VHDL code for Parallel In Parallel Out Shift Register All About FPGA www.

Vhdl program for left shift register manual#

Vhdl program for left shift register how to#

The following example shows how to write the program to incorporate multiple components in the design of a more complex circuit. VHDL code for Parallel-In Serial-Out (PISO) shift register See also: VHDL codes for flip flops, latches. Saturation arithmetic is a version of arithmetic in which all operations, such as addition and multiplication, are limited to a fixed range between a. I can make a right shift using example code as follows and it works. I have created code for 8 bit shift register left. A shift register can be initialized in VHDL or Verilog code for both synthesis and simulation. For parallel in parallel out shift registers, all data bits appear on the parallel outputs immediately following the simultaneous entry of the data bits.

A shift register has the capability of shifting the data stored in the register from left to right or right to left. There are 3 methods to shift bits left in VHDL: 1. Two different ways to code a shift register in VHDL are shown. So far I believe to have made a 1- bit register, here is my code: LIBRARY ieee. Ive implemented a shift left register with serial input and parallel output using a 'slice' to implement the shift but I cant figure out how to implement the same logic using an overloaded shift operator: sll (shift left logical) operator. Main inputs of the register include clock (clk), clear (clr), load/enable(ld) signals and an n- bit data (d). I'm having some troubles in designing a 1- bit and 3.

Register Design in VHDL - Stack Overflow.

0 kommentar(er)

0 kommentar(er)